[Teledyne LeCroy] ‘어떤 CA(command address) 프로빙이 필요하지?’’ 주제의 포스팅

- 2024-11-12

- 조회수784

[Teledyne LeCroy] ‘어떤 CA(command address) 프로빙이 필요하지?’’ 주제의 포스팅

지난 포스팅에서는 DDR 버스트 신호를 분석할 때, 텔레다인르크로이 DDR Debug툴킷은 READ와 WRITE 버스트를 3 가지 방법으로 구분한다고 말씀드렸습니다. 이번 포스팅에서는 Read와 Write를 가장 정확하게 구분할 수 있는 Command Bus를 이용할 때 최소한 으로 필요한 라인은 무엇인지 알아보겠습니다.

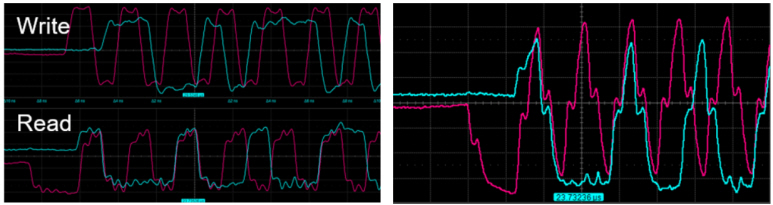

DDR 신호 측정시 Read, Write를 구분하는 방법은 위상차 이용법, command bus, CA4+latency를 이용하는 방법 3가지와 LPDDR에서는 preamble을 이용하는 구분하는 방법이 있습니다. 가장 간단한 방법은 데이터(DQ)와 스트로브(DQS) 라인들의 에지 위상차를 사용하여 READ와 WRITE 버스트를 구분하는 방법입니다. 이 방법은 버스트의 구분이 간단하여 테스트하려는 신호만 있으면 Read, Write 구분이 가능하다는 것입니다. 단점이라면 신호에 노이즈, 반사가 많이 포함되어 있고 상승 시간, 하강 시간이 느려진 신호에서 위상을 측정하게 되면 버스트 분리 방법이 신뢰하기 어려워진다는 것입니다. 그림 1의 오른쪽에는 신호에 반사가 포함되어 Read, Write를 구분하기가 쉽지 않습니다.

그림 1. DQ와 DQS의 위상 차를 통해 Read, Write 구분(왼쪽), 오른쪽 신호의 경우 반사가 많이 포함되어 위상으로 구분하기 어려움.

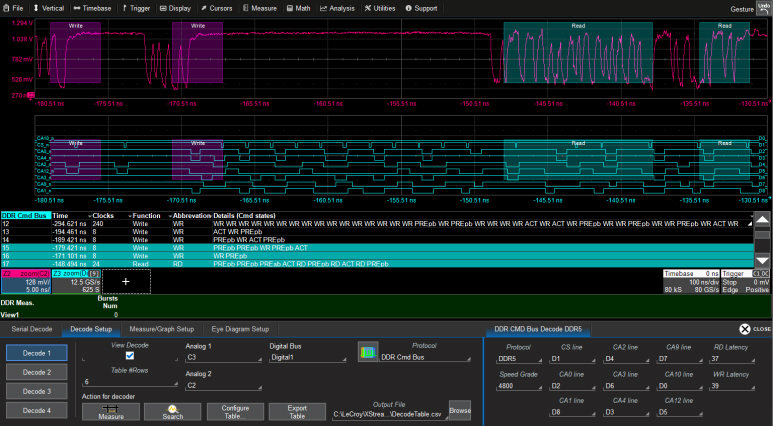

Read, Write 버스트를 구분하는 가장 확실한 방법은 커맨드 버스를 이용하여 신호를 포착하고 트리거하는 방법입니다. 이 방법은 버스트 종류에 대한 불확실성을 제거할 수 있습니다. 이 방법의 장점은 버스트 분리 방식의 신뢰성이 높을 뿐 아니라 커맨드 버스의 동작과 DQ/DQS와의 연관성을 동시에 확인하는 통찰력을 제공한다는 점입니다. 약간의 불편한 점이 있다면, 커맨트 버스 오실로스코프에서 확인할 수 있도록 HDA125의 리드셋을 추가적으로 프로빙 해야 한다는 것입니다.

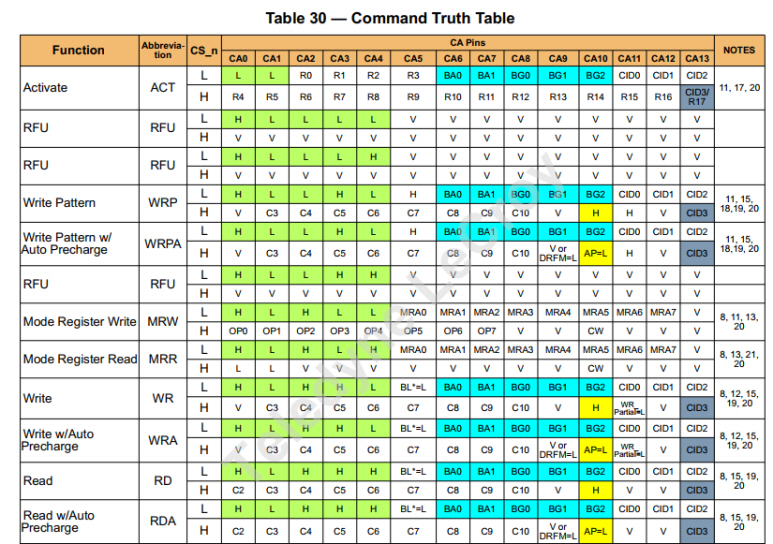

그림 2의 테이블은 2024년 4월에 릴리즈된 JESD79-5C.01_v1.31 문서에서 복사한 DDR5 SDRAM의 진리표입니다. CA(Command Address) 상태 조합으로 Read, Write 뿐만아니라 다른 기능들 또한 설명되는 것을 알 수 있습니다.

그림 2. JEDEC 표준에서 발췌한 DDR5 진리표

최소한의 Command Addreaa

HDA125를 사용하여 할 때 프로빙할 디지털 신호는 각 JEDEC 사양에 고유한 Command Truth Table에 따라 달라집니다. 텔레다인르크로이의 DDR 디버그 툴킷으로 디코딩하는 경우에도 DDR의 각 사양별 진리표를 확인하여 프로빙하는 것이 확실하며, 아래의 표에서는 HDA125에서 command bus를 이용하여 트리거 또는 Read, Write를 구분할 때 사용하는 command bus 신호입니다. 별표(*)가 표시된 신호는 R/W 분리에 필요한 최소 신호입니다.

그림 3. 진리표에 따라 CA라인을 프로빙하여 디코딩한 예. DDR Debug 툴킷에서는 CA라인 지정 및 +/- 인버트 기능을 제공합니다.